在當今萬物互聯的時代,“低功耗”已從一個技術術語演變為驅動眾多行業創新的核心關鍵詞。它不僅關乎設備的續航能力,更深層次地影響著物聯網(IoT)的架構、成本、部署規模乃至商業模式。本文將深入解析低功耗的內涵,并聚焦其在物聯網技術研發中的最新動態與應用。

一、什么是低功耗?

“低功耗”并非簡單的“省電”,而是一個系統性的工程技術概念。它指的是在保證設備或系統完成特定功能、達到所需性能指標的前提下,通過硬件設計、軟件算法、系統架構等多維度的優化,將電能消耗降至最低水平。其核心目標是在有限的能源供給(如小型電池、能量收集裝置)下,最大限度地延長設備的工作壽命,或降低對電網的依賴。

實現低功耗是一個復雜的系統工程,通常涉及以下幾個層面:

- 硬件層:采用低功耗的微控制器(MCU)、傳感器和通信芯片;優化電源管理電路,如使用高效率的DC-DC轉換器、動態電壓頻率調節(DVFS)技術;選擇漏電流極低的半導體工藝。

- 軟件與算法層:設計智能的休眠-喚醒機制,讓設備在絕大部分時間處于極低功耗的休眠狀態,僅在需要時快速工作;優化數據處理與傳輸算法,減少不必要的計算與通信開銷。

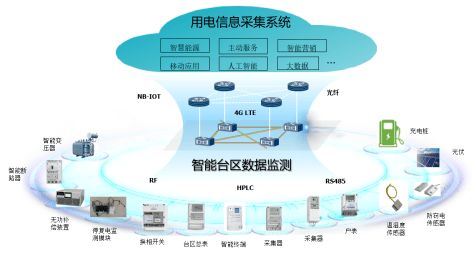

- 系統與網絡層:在物聯網系統中,采用低功耗廣域網(LPWAN)等專為低流量、長距離、電池供電設備設計的通信協議;設計高效的路由與網絡拓撲,減少中繼能耗。

二、低功耗技術的最新報道與趨勢

低功耗技術的發展日新月異,尤其在物聯網領域涌現出許多令人矚目的進展:

- 超低功耗處理器的突破:各大芯片廠商(如ARM、Silicon Labs、STMicroelectronics)不斷推出新一代超低功耗MCU。這些芯片在深度睡眠模式下的功耗已降至微安(μA)甚至納安(nA)級別,而喚醒時間卻縮短到微秒級,實現了“常感知、常關閉”的理想狀態。RISC-V開源架構的興起,也為定制化、極致優化的低功耗處理器設計提供了新路徑。

- 能量收集技術的成熟與集成:單純依賴電池已無法滿足海量、長期部署的物聯網節點需求。將環境中的光能、熱能、振動能、射頻能等微弱能量收集起來,為設備供電的“無電池物聯網”正從概念走向現實。最新的系統級芯片(SoC)已開始集成能量管理單元,能夠高效管理收集到的毫瓦級能量,實現設備的永久或半永久性自供電。

- 低功耗AI的邊緣化部署:在終端設備上直接運行輕量級人工智能模型(TinyML),進行本地數據識別與決策,避免了將海量原始數據上傳至云端所帶來的巨大通信能耗。專為邊緣AI設計的低功耗神經網絡加速器(NPU)正成為新一代物聯網芯片的標準配置,使得智能感知在功耗預算內成為可能。

- 新一代LPWAN技術的競爭與融合:NB-IoT和LoRa作為兩大主流LPWAN技術,持續在覆蓋、容量、功耗和成本上優化。諸如MIoTy、Sigfox等標準也在特定領域深耕。最新的趨勢是技術的互補與融合,例如支持多模通信的芯片,允許設備根據場景在不同網絡間智能切換,實現全局能耗最優。

三、物聯網技術研發中的低功耗核心挑戰與方向

面向未來的物聯網研發,低功耗仍然是重中之重,并呈現出以下幾個關鍵研發方向:

- 全生命周期功耗優化:研發重點從單一器件的低功耗,轉向涵蓋“感知-計算-通信-存儲”全鏈路的協同優化。例如,研究如何在傳感器端進行模擬前端預處理,減少需要數字化處理的數據量;探索近內存/存內計算架構,打破“內存墻”帶來的功耗瓶頸。

- 智能與功耗的平衡藝術:隨著應用對智能需求的提升,如何在有限的能量預算內嵌入更強大的處理能力,是永恒的挑戰。研發更高效的稀疏神經網絡模型、事件驅動型傳感與計算范式(只在有事件發生時工作),是當前的熱點。

- 安全與功耗的共生:為物聯網設備添加加密、認證等安全功能必然會增加功耗。研發輕量級密碼學算法、硬件安全模塊以及低開銷的安全協議,實現安全與低功耗的“魚與熊掌兼得”,是保障物聯網大規模可靠應用的前提。

- 標準化與生態構建:低功耗的成功離不開整個生態系統的支持。推動功耗評估標準、測試方法的統一,以及開發工具鏈、操作系統(如Zephyr OS)的優化,能極大降低開發門檻,加速低功耗物聯網方案的落地。

###

低功耗技術是物聯網從藍圖變為普適性基礎設施的基石。它不再是一個孤立的技術指標,而是貫穿于芯片、網絡、算法與系統設計的核心哲學。最新的研發進展正推動物聯網設備向更長壽、更智能、更自主的方向演進。隨著材料科學(如二維半導體)、通信技術(如反向散射通信)和架構創新的持續突破,低功耗的極限將被不斷刷新,從而解鎖更多前所未有的物聯網應用場景,真正構建一個高效、可持續的智能世界。